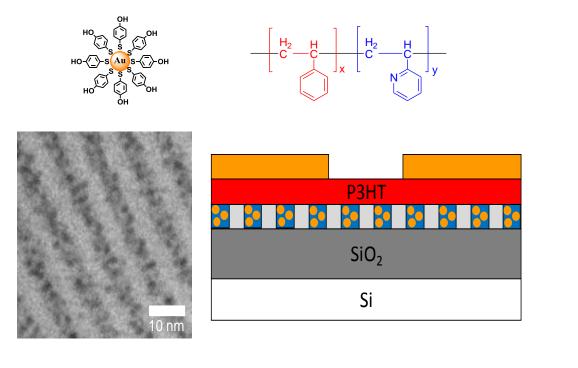

Floating Gate Memory via Additive Driven Assembly: Opportunities for Device Fabrication using Solution Processing and Roll-to-Roll Manufacturing

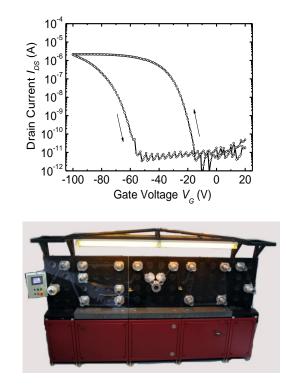

We have used additive driven self-assembly to create the active device layer for floating gate memory. This approach, which allows for very high loadings of 2 nm gold nanoparticles in a polystyrene-block-poly(vinyl pyridine) block copolymer, offers theoretical storage capacities competitive with current flash memory devices. To achieve high storage densities in devices, device level patterning at micron and smaller length scales is required. We are currently pursuing the device patterning via roll-to-roll (R2R) nanoimprint lithography. These technologies will enable the production of memory and other devices using low cost, sustainable, nanomanufacturing.

Professors James J. Watkins and Alejandro L. Briseno, University of Massachusetts

This work supported by The Center for Hierarchical Manufacturing at the University of Massachusetts Amherst CMMI-1025020