# Design, Fabrication, Assembly and Characterization of a SWNT Switch for Non-volatile Memory Applications

Sivasubramanian Somu, Taehoon Kim, Peter Ryan, Luciano Silvestri, Ahmed Busnaina, Nick McGruer & George Adams

### **Director: Ahmed Busnaina, NEU**

Deputy Director: Joey Mead, UML, Associate Directors: Carol Barry, UML; Nick McGruer, NEU; Glen Miller, UNH; Jacqueline Isaacs, NEU

### **Outline**

- > State of Art

- Bi-stable Switch-Principle of Operation

- > Fabrication

- Directed Assembly

- Actuation

- Product Attributes

- > Summary

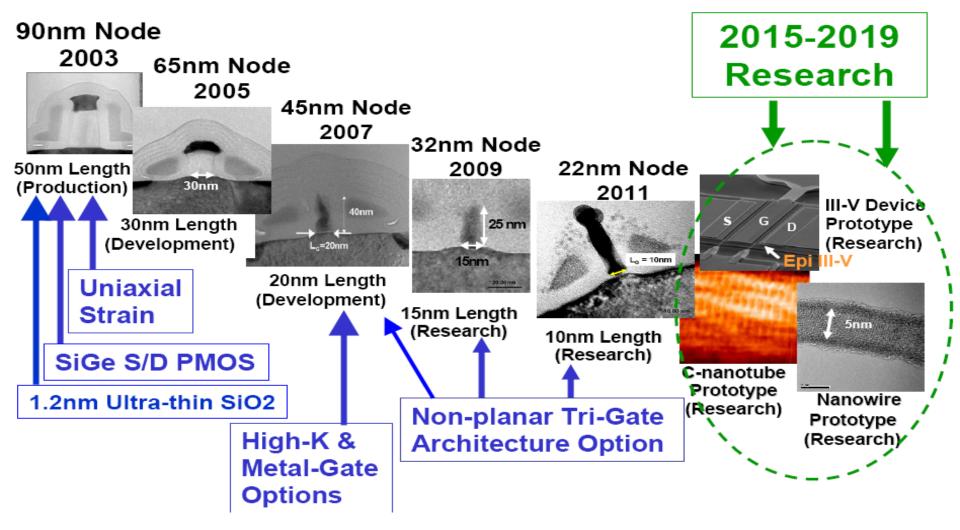

# **Beyond the ITRS Road map?**

### Transistor Scaling and Research Roadmap

### **CMOS Scale Limits and Power Considerations**

### CMOS is projected to be with us for the next 15 years.

# Theoretical<sup>1</sup> parameters at $T=T_{room}$ characteristic dimension of 1.5 nm, switching energy of 0.017 eV switching speed of 0.04 pico sec.

### Theoretical<sup>1</sup> results:

1% duty cycle &

1% active transistors

Heat generated is ~ 370W/cm<sup>2</sup>

1. Zhirnov, V., et. al., Proceedings IEEE, Nov. 2003

### Nanoelectronics Challenges Examples of Non-Charge Based Switches

# Novel Devices What are we looking for?

- Required characteristics:

- Scalability

- Performance

- Energy efficiency

- Gain

- Operational reliability

- Room temp. operation

- Preferred approach:

- CMOS process compatibility

- CMOS architectural compatibility

### Alternative state variables

- Spin–electron, nuclear, photon

- Phase

- Quantum state

- Magnetic flux quanta

- Mechanical deformation

- Dipole orientation

- Molecular state

# NEMS-Non volatile Design

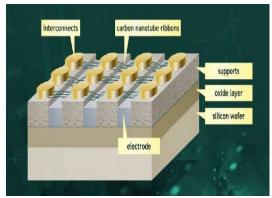

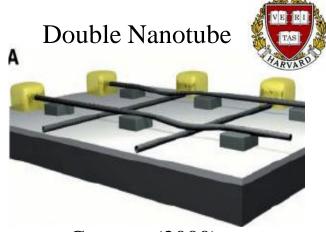

### **NRAM**

- •Product (2004)

- •SWNT Fabric

- •Spin coated (Room Temperature)

$V_{Read} < 1.5 \text{ V}; R_{ON}/R_{OFF} \sim 10^5$

- •Concept (2000)

- •Two single SWNT

Expected  $V_{Read} < 100 \text{ mV}$ ;  $R_{ON}/R_{OFF} \sim 10^5$

NEMS → Memory & Embedded Applications.

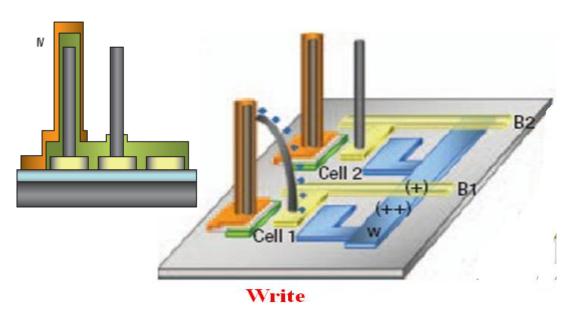

# NEMS-Principle of operation

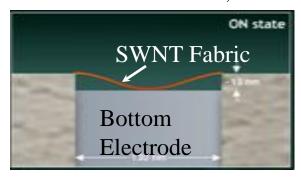

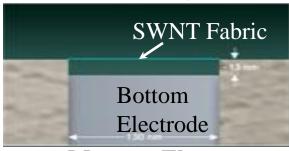

### **NRAM**

#### **WRITE**

V<sub>write</sub>=7V, Closed Circuit → R<sub>Low</sub> van der Waals attraction,

#### **ERASE:**

V<sub>Erase</sub>=30V Open Circuit → R<sub>High</sub>

•Memory Element

### **DOUBLE NANOTUBE**

#### **WRITE**

$V_{\text{write}}$ =4.5V, Closed Circuit  $\rightarrow$   $R_{\text{Low}}$ van der Waals attraction,

#### **ERASE**:

V<sub>Erase</sub>=20V Open Circuit → R<sub>High</sub>

•Memory Element

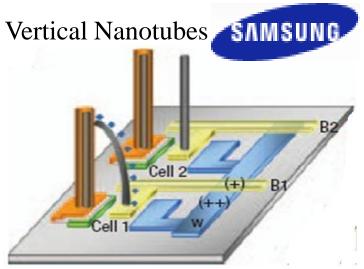

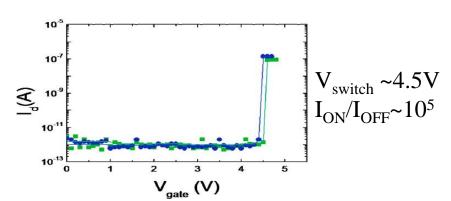

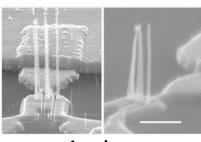

# NEMS-Volatile Design

- Research Prototype 2005

- Capacitive based

- MWNT Pillars

- CVD grown (High Temperature)

- Research Prototype 2004

- Resistive based

- MWNT

- Spin coated & CVD growth

NEMS → Embedded Applications. → Expected to replace DRAM

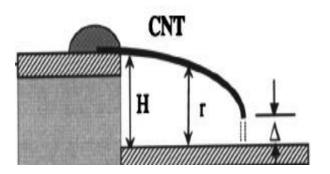

# NEMS-Principle of operation

### Vertical Nanoswitch:

### Write:

Apply 0.1V to Drain; Apply gate voltage to the 4.5V

- →CNT of Drain begins to bend and contacts the source

- → Capacitor gets charged

### Erase:

Removal of gate voltage → Repulsive electrostatic force Drain nanotube springs back. → Capacitor Discharges

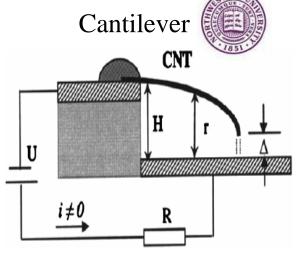

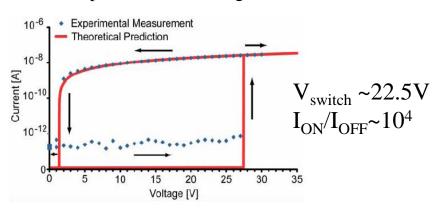

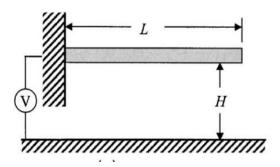

### **NEMS** Cantilever

### Write:

22V, tunneling current, 0.7nm gap

### Erase

<2V, open circuit 100nm gap

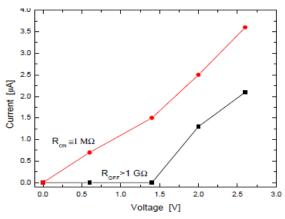

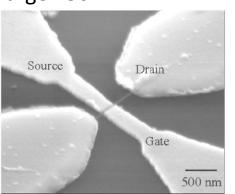

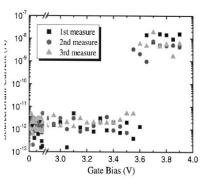

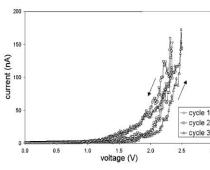

# NEMS – State of the Art

### Large ~30nm MWNT

### Only 3 Sweeps!

S. N. Cha, J. E. Jang, Y. Choi, G. A. J. Amaratunga, D. J. Kang, D. G. Hasko, J. E. Jung, and J. M. Kim, "Fabrication of a nanoelectromechanical switch using a suspended carbon nanotube," *Applied Physics Letters*, vol. 86, p. 083105, 2005.

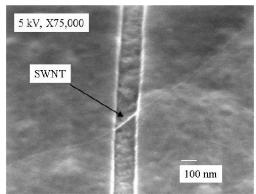

### **Serial Process SWNT**

Only 3 Sweeps!

A. B. Kaul, E. W. Wong, L. Epp, and B. D. Hunt, "Electromechanical carbon nanotube switches for high-frequency applications," *Nano Lett, vol. 6, pp. 942-947, 2006.*

### **Huge 70nm MWNTs**

### V<sub>2nd</sub>=0.05V V<sub>2nd</sub>=0.05V V<sub>2nd</sub>=0.05V V<sub>2nd</sub>=0.05V

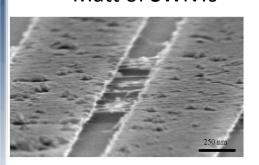

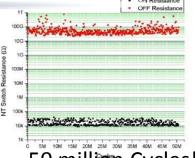

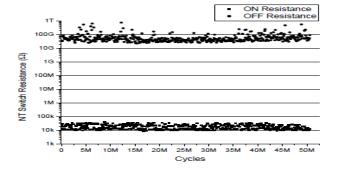

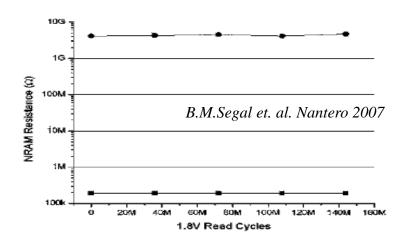

### Matt of SWNTs

50 million Cycles! ~10ns Response Time

R. F. Smith, T. Rueckes, S. Konsek, J. W. Ward, D. K. Brock, and B. M. Segal, "Carbon nanotube based memory development and testing," 2007, pp. 1-5.

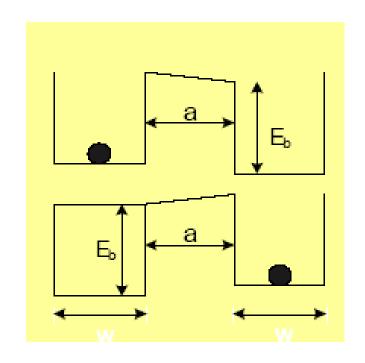

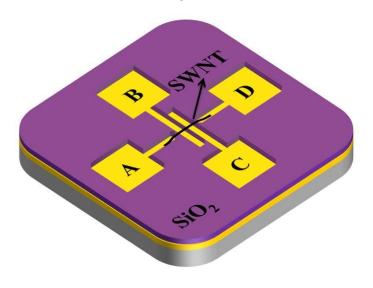

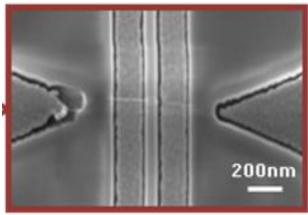

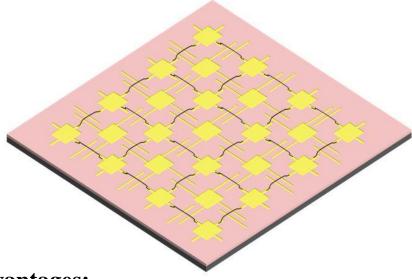

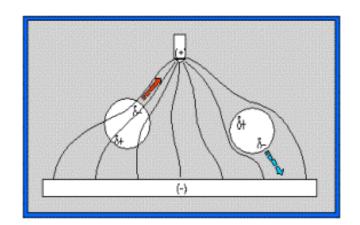

# Bistable Nano Electromechanical Switch

### Bistable SWNT Nanoswitch

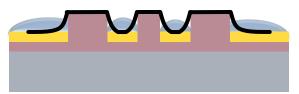

### Schematic diagram

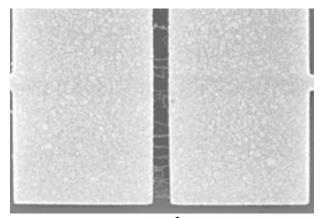

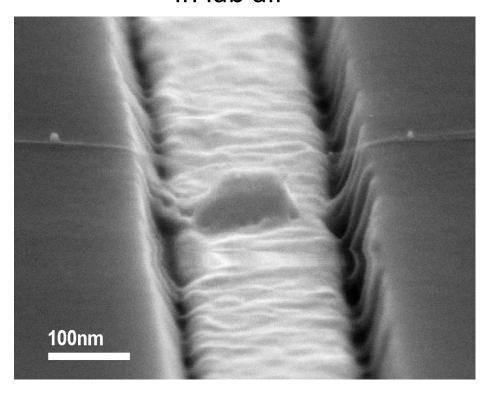

Top View of fabricated device

Switch array schematic

### **Advantages:**

- Non charge based device

- Non volatile

- Minimal fabrication steps

- Operational frequency in terahertz

- Stand alone RS flip Flop

- Radiation hard

- Very robust.

- •Switching at the same vo

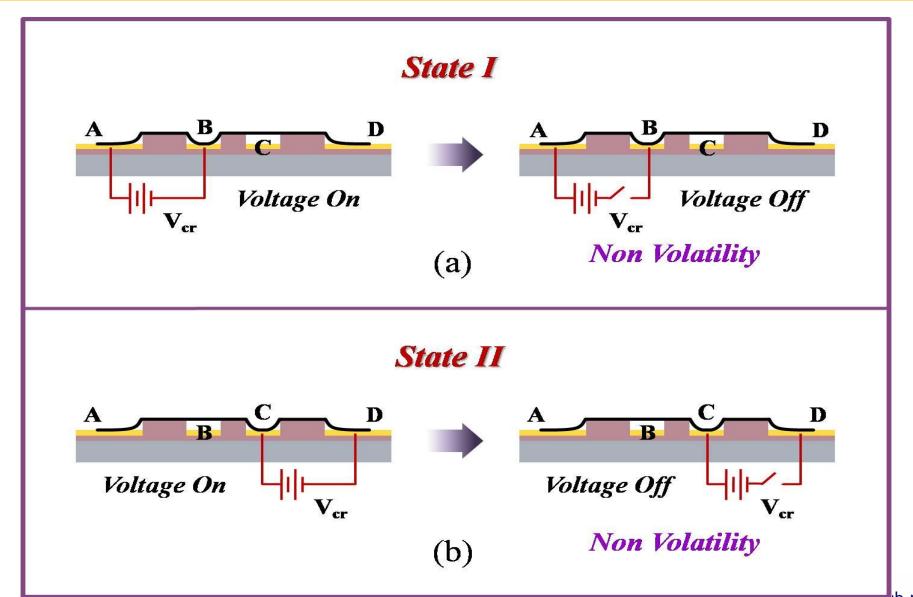

# Principle of Operation

Nanomanufacturing

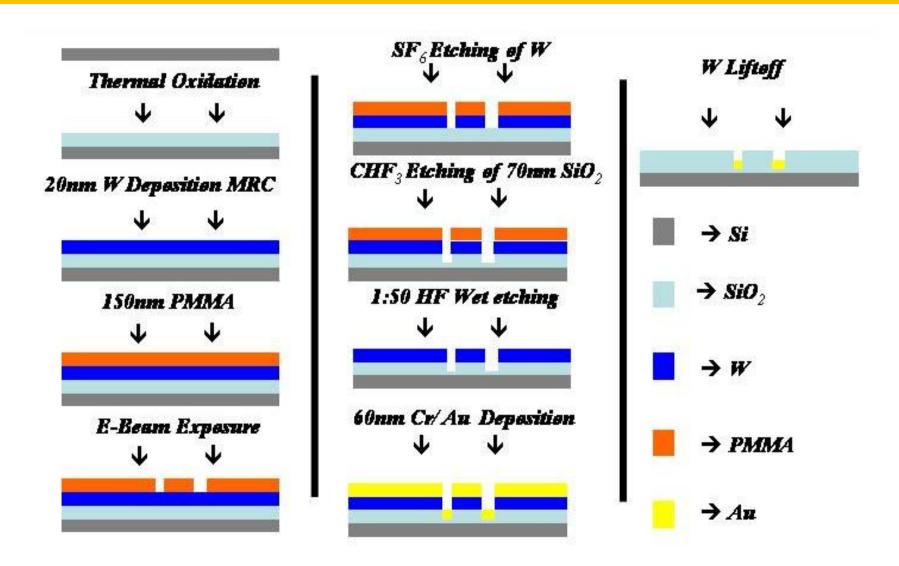

## Template Fabrication

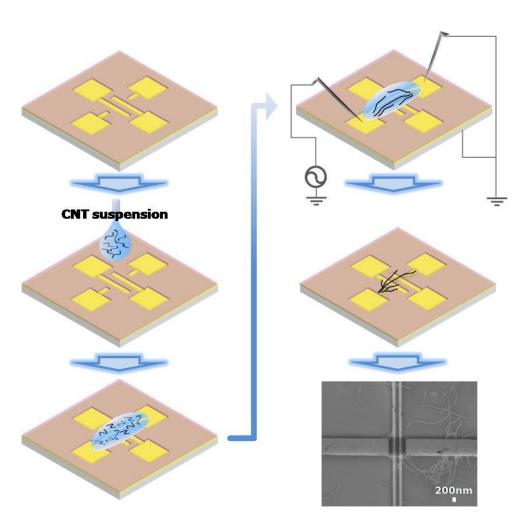

# Directed assembly of SWNT

Dielectrophoretic force (F<sub>DEP</sub>)

$$F_{DEP} = \frac{\pi}{6} r^2 l \epsilon_m Re \{ K(\omega) \} \nabla E_{rms}^2$$

$$K(\omega) = \left(\frac{\varepsilon_{p}^{*} - \varepsilon_{m}^{*}}{\varepsilon_{m}^{*}}\right)$$

I: Length of rod-like particle, r: Radius of rod-like particle

$\epsilon_m$ : Real permittivity of suspending medium

E<sub>rms</sub>: Root mean square (rms) of the electric field

$K(\omega)$ : Clausius-Mosotti factor

• DEP force strongly depends on the electric field gradient,  $\Delta E_{rms}$ .

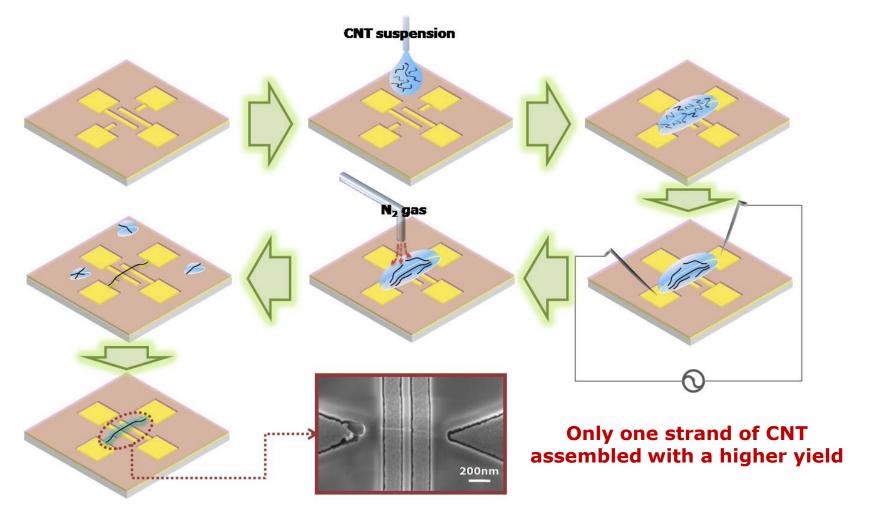

### Conventional Dielectrophoretic Assembly Process of CNT

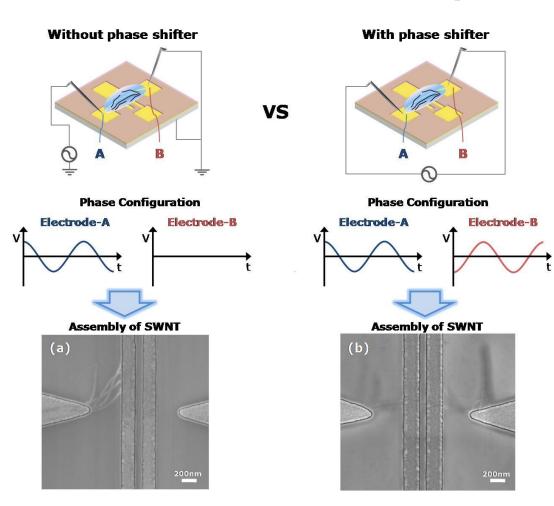

- ✓ Changed the electrode configuration.

- ✓ Introduced a phase shifter at the ground electrode with the potential being opposite in phase with that of the phase electrode.

- ✓ Drying a drop of CNT solution by employing stream line of N₂.

### Modifications of Assembly Process of CNT

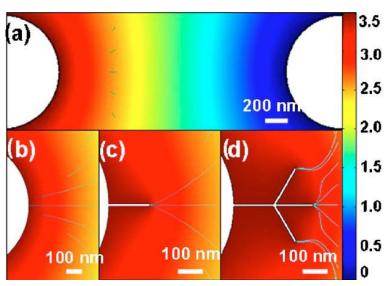

Simulation

### Changes of the electrode configuration:

- (a) initial

- (b) transition

- (c) final

### Modifications of Assembly Process of CNT

Results of introducing a phase shifter at the ground electrode (electrode-B) being opposite in phase with that of the phase electrode (electrode-A)

### Modified Dielectrophoretic Assebmly Process of CNT

Problem: For a shallow trench during drying process the surface tension of the liquid (water) pulls in the SWNT into the trench causing short circuited.

Use a Critical point Dryer (CPD).

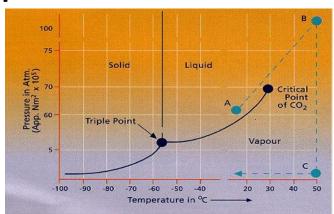

### Critical Point Dryer

- √ To make CNTs suspended above trenches

- ✓ Dry process at critical point in CO₂ phase diagram

- √ No phase transition

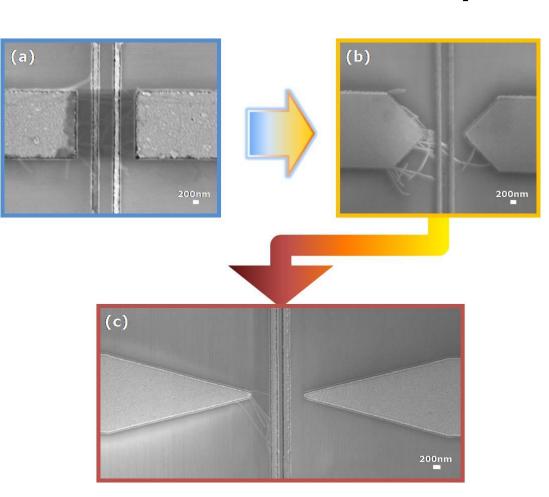

# Actuation Preliminary Results

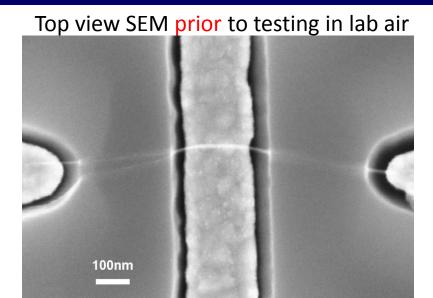

### **Actuation in Ambient Conditions**

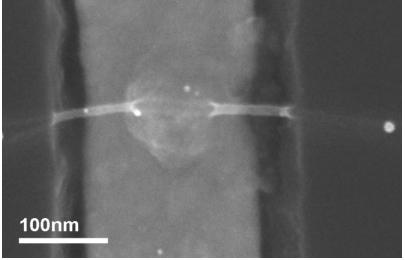

Top/view SEM after testing in lab air

80 Degree SEM after testing in lab air

- → Organic contamination build up

- → Device needed to be tested in

Nitrogen enviro

Center for High-rate Nanomanufacturing

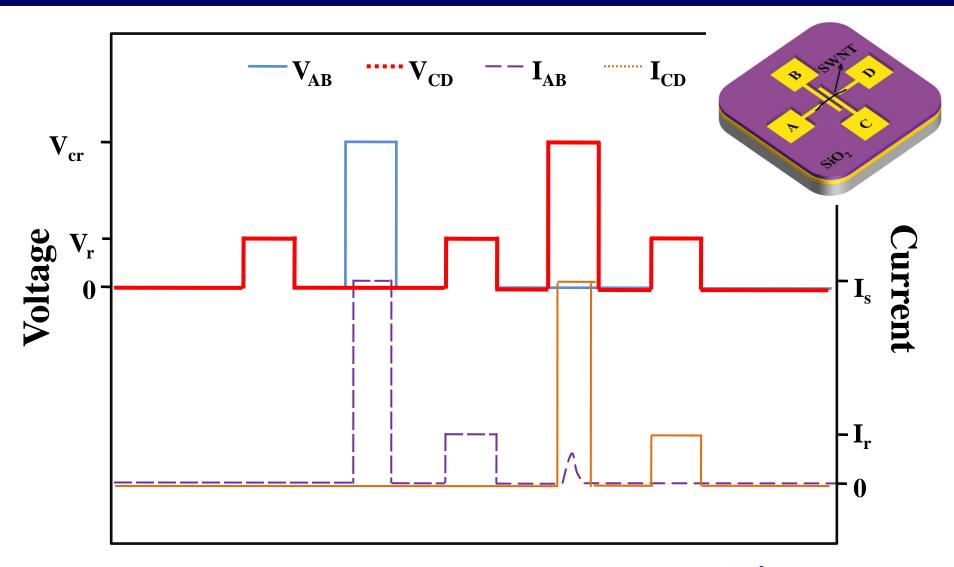

# **Actuation Schematic**

# Product Attributes

### **Product Attributes**

### Bit density: Current Status (Concept; Prototype; Production)

|                 | NRAM                   | Bistable<br>Nanoswitch | Cantilever            | Vertical<br>Nanoswitch | Double<br>Nanotube*    | NAND<br>Flash          |

|-----------------|------------------------|------------------------|-----------------------|------------------------|------------------------|------------------------|

| Feature Size    | 180nm                  | 180nm                  | 500nm                 | No Data                | 10nm                   | 40nm                   |

| Factor          | 6F <sup>2</sup>        | 12F <sup>2</sup>       | 6F <sup>2</sup>       | No data                | 6F <sup>2</sup>        | 4F <sup>2</sup>        |

| Cell Size       | 0.19µm <sup>2</sup>    | $0.38\mu m^2$          | 1.5µm <sup>2</sup>    | No data                | 0.0006µm <sup>2</sup>  | $0.0064 \mu m^2$       |

| Storage density | 3.09Gb/in <sup>2</sup> | 1.55Gb/in <sup>2</sup> | 0.6Gb/in <sup>2</sup> | 2.5Gb/in <sup>2</sup>  | 1000Gb/in <sup>2</sup> | 62.9Gb/in <sup>2</sup> |

<sup>→</sup> Cell factor remains same with scaling down

### **Power Consumption**

| Energy/<br>Power | NRAM    | Bi stable | Cantilever | Vertical<br>Nanoswitch | Double<br>Nanotube* | NAND Flash |

|------------------|---------|-----------|------------|------------------------|---------------------|------------|

| Read             | 1.5fJ/  | 1.5fJ/    | 0.25fJ/    | 1zJ-0.16fJ/            | 1.5fJ/              | 0.165nJ/   |

|                  | 0.15 μW | 0.15 μW   | 0.025μW    | 1pW-0.1μW              | 0.15 μW             | 3300 μW    |

| Write            | 7fJ/    | 4.5fJ/    | 2.3fJ/     | 7.2fJ/                 | 4.5fJ/              | 1.87nJ/    |

|                  | 0.7μW   | 0.45μW    | 0.23 μW    | 4.5 μW                 | 0.45μm              | 2 μW       |

| Erase            | 30fJ/   | 4.5fJ/    | 2zJ/       | 160zJ/                 | 20fJ/               | 0.33nJ/    |

|                  | 3 μW    | 0.15 μW   | 0.2pW      | 1pW                    | 2 μW                | 3.3 μW     |

<sup>→</sup> Power decreases non-linearly with scaling down

<sup>\* →</sup> Has never been fabricated (estimated values)

<sup>\* →</sup> Estimated values

### Product Attributes

### Read, Write, Erase Time

→ High speed, faster than flash and comparable to SRAM

→ Speed increases non linearly with scaling down

| Speed | NRAM | Bistable | Cantilever | Vertical<br>Nanoswitch | Double<br>Nanotube* | NAND Flash     |

|-------|------|----------|------------|------------------------|---------------------|----------------|

| Read  | 10ns | 10ns     | 1-10ns     | 1.3ns-16ns             | 0.01ns              | 30μs/4224bits  |

| Write | 10ns | 10ns     | 1-10ns     | 1.3ns-16ns             | 0.01ns              | 200μs/4224bits |

| Erase | 10ns | 10ns     | 1-10ns     | 1.3ns-16ns             | 0.01ns              | 2ms/135168bits |

→ Non destructive read (No rewrite)

\*

Have never been fabricated (estimated values)

### **Endurance**

- Devices have cycled ~ 5X10<sup>7</sup> for Write/Erase and

- ~1.5X10<sup>8</sup> Read with no failure issues.

- •Others devices are expected to have similar

endurances.

NAND write and erase is in Pages and Blocks

Flash endurance is only 10<sup>5</sup> cycles

### Summary

- > Have fabricated a Bi-stable switch for memory and logic application

- > Employed a modified Dielectrophoresis process for assembly of SWNTs

- > Switch actuation showed that the switch is nonvolatile

- > Switch actuation showed that the switch is indeed bi-stable

- > Switch actuation is carried out at low voltage (~5V)